## Integration of Various Types of Compensated Dielectric Bridges for mm Coplanar Applications.

L. Stephan, J. Ph. Coupez, E. Rius, C. Person, S. Toutain

Laboratoire d'Electronique et Systèmes de Télécommunications (L.E.S.T.) - URA CNRS n° 1329

U.B.O.- 6, av. Le Gorgeu - BP 809 -29285 BREST CEDEX-FRANCE-Tel : 98 01 61 26-Fax : 98 01 63 95

ENSTBr - BP.832 - 29285 BREST CEDEX-FRANCE-Tel : 98 00 13 68-Fax : 98 00 13 43

**ABSTRACT :** This paper describes a new approach in the realization of integrated dielectric bridges for uniplanar technology. It shows how the electrical characteristics of a CPW are disturbed and how these parasitic effects may be compensated by simply modifying the strip width of the transmission line. Based on this approach several solutions are presented. Theoretical results (static analysis) and experimental results ("on wafer" measurements, 1 GHz - 50 GHz) are compared. In order to verify the efficiency of these dielectric bridges, filtering structures are tested.

### Introduction

Many works have shown that the coplanar waveguide is a guided medium which can be considered as an alternative to microstrip lines in millimeter frequency range. Indeed, the uniplanar technology permits a high integration level, and is well-suited for high frequency applications because of the minimisation of the parasitic effects for both elements interconnection and integration of active components. As all the conductors are in the same plane, the ground connections through via holes are eliminated, so resulting in a significant manufacturing process simplification. Both series and shunt passive or active components are implementable, which results in a great flexibility for circuit design procedure. Furthermore, the variation of the slot and the strip widths offers one more degree of freedom in the line synthesis, once the substrate height is chosen, than microstrip line.

However, there is one major drawback in dealing with coplanar design. The parasitic coupled slot-line mode is excited by nonsymmetrical CPW discontinuities such as bends and T-junctions for example. As both, even- and odd-modes, are fundamental modes in the coplanar waveguide, it is

necessary to eliminate one of them : the coupled slotline mode. This is made by bridges which insure the same potential on each side of the ground plane.

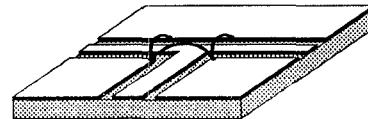

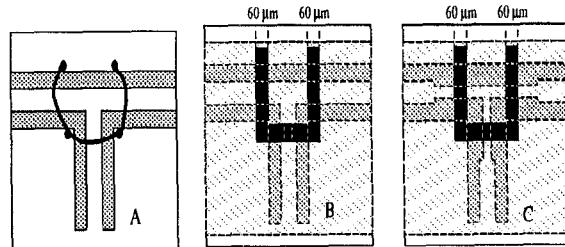

At the present time, for MIC circuits, the bridges are made by thin metallic wires ( $\phi \approx 25 \mu\text{m}$ ) which are bonded on the ground planes (Fig. 1). Such an operation implies numerous problems in repetitivity and positioning which deteriorate the circuits performances. Moreover the fragility of such bridges doesn't insure the reliability of the circuit.

In order to overcome these problems, we proposed a new multilayer uniplanar approach for the bridges integration, with compensation techniques for the parasitic effects. Even if this approach has been tested in a mm MIC technology, it appears also suitable for mm MMIC applications.

Fig. 1 : Bounding wires on a T-junction

### The thick film multilayer uniplanar technology

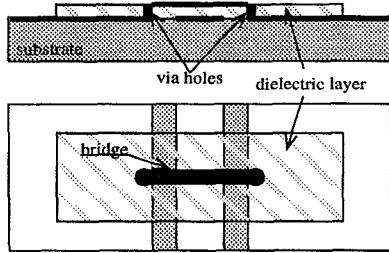

As shown in figure 2, the multilayer uniplanar technology consists in the deposit of a dielectric layer ( $\approx 20 \mu\text{m}$  two layers thickness) with a thick film technological process. This layer can be local or global over the first conductive level. Via holes are made in this dielectric layer, in order to assure an electrical contact between the two ground planes and the bridge pattern, which is directly screen printed or screen printed and etched on the top of the dielectric layer. With the available photo imageable commercial dielectric materials, the resolution of the via holes is better than  $40 - 50 \mu\text{m}$ . In our case, the material which has been used, is a KONSERQ product (KQ 110) with a low

permittivity value of 3.9 and dielectric losses of  $5 \cdot 10^{-5}$  [1]. Low loss propagation has been constated over a large frequency band (1 GHz - 50 GHz) by "on wafer" measurements on very simple structures.

Finally, such a process leads to get robust integrated bridges and eliminates the problems in positioning and repetitivity.

Fig. 2 : Dielectric bridge in multilayer uniplanar technology

### Parasitic influences of the bridges

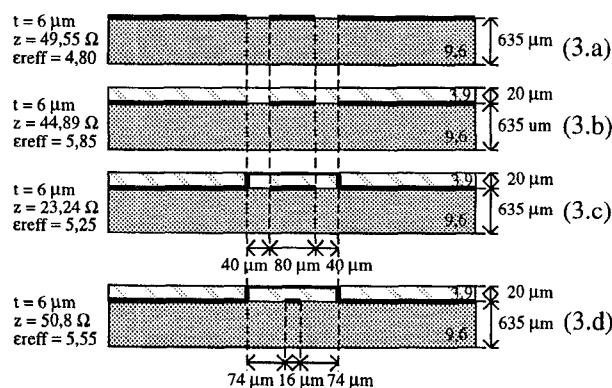

According to the low height of the dielectric layer, a significant additional capacitance per unit length is located between the inner conductor of the CPW and the short-circuited strip. Obviously, the characteristic impedance and the effective dielectric constant are considerably modified in the bridge region. Taking into account the low dispersive character of the coplanar technology, these variations can be calculated in first approximation with the static finite difference method [2].

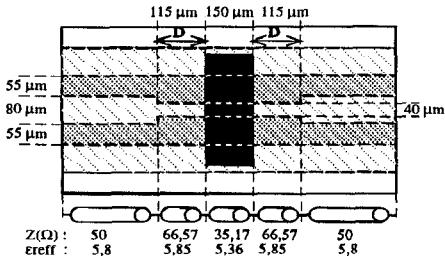

Fig.3 : Electrical parameters of the technology

The figure 3 shows the influence of the dielectric layer (Fig. 3.b) and of the dielectric bridge (Fig. 3.c) on the electrical parameters of a  $50 \Omega$  CPW (Fig. 3.a).

Related to these numerical data, this type of dielectric bridge is a severe discontinuity for the CPW. Fortunately, the total length of a dielectric

bridge is typically small ( $\approx 50 \mu\text{m}$ ) and the influence of one single bridge on the transmitted RF power remains negligible (under 40 GHz). However, for practical uniplanar designs a large number of bridges is necessary leading to an accumulation of parasitic effects on the CPW.

### The compensated bridges

#### Based on "all pass filter" concept

In order to minimize the distortion due to the low characteristic impedance of the bridge discontinuity, the inner conductor's width under the bridge can be locally reduced. By this mean, it is possible to match the electrical parameters of the transmission line, by increasing the inductance per unit length of the bridge and by reducing the capacitance per unit length of the bridge. An all-pass filter is then realised.

Unfortunately this method is no satisfactory for several reasons. From a technological point of view, some difficulties appear (under-etching, precision, repetitivity ...) in making very tiny strips as shown in figure 3.d. Moreover, in the case of a very tiny bridge the positioning of this one is crucial. On the other hand this will lead to an increasing resistance per unit length of the bridge, which will cause additional losses [3]. So to overcome these problems, we propose the implementation of compensated bridge structures.

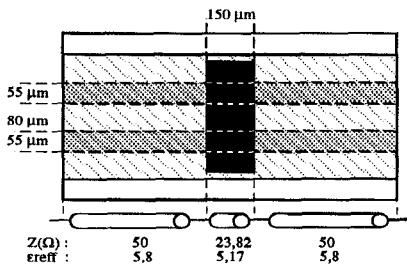

#### Based on "low pass filter" concept

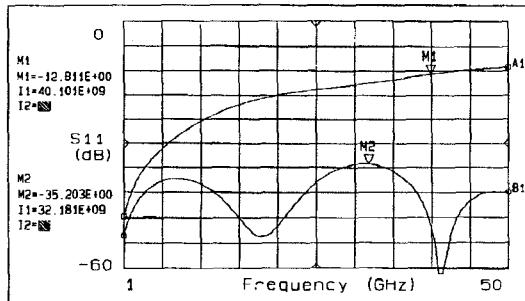

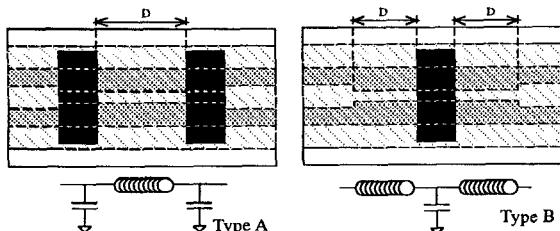

The basic idea is to use high characteristic impedance apart the bridge in order to compensate the low characteristic impedance of this one. This can be done by reducing the width of the inner conductor's under the bridge and of each side of this one on a length D. By varying the length D of this compensation, it's possible to match the bridge connected on the CPW. then, a low-pass filter with a very high cut off frequency, according to the low LC values is realised. The main advantage of this type of structure is the reduction of technological constraints. It's not necessary to build very tiny strips and the positioning of the bridge is not crucial. For instance, the figure 4 shows the theoretical return losses of a CPW with an uncompensated bridge (Fig 4.a) and with a compensated bridge (Fig 4.b). In the simulated electrical model, each region is replaced by a correspondant transmission line.

(Substrate :  $\epsilon_r = 9.6$ , thickness  $635 \mu\text{m}$  / Dielectric

layer :  $\epsilon_r = 3.9$ ,  $h = 20 \mu\text{m}$ )

Fig. 4.a : Uncompensated bridge

Fig. 4.b : Compensated bridge

Fig. 4.c : Return losses

The results show both, the non negligible parasitic influence of the bridge and the real efficiency of this compensation technique in a wide frequency band. Based on a similar approach, the structure composed of two bridges separated by a compensation circuit can be realized. Results are equivalent in the two cases.

Fig. 5 : Compensated bridges model's

### Experimental results

In order to validate these ideas, a great variety of different dielectric bridges (with and

without compensation) on various types of CPW and resonators has been built on an alumina substrate ( $\epsilon_r = 9.6$ , thickness = 635  $\mu\text{m}$ ). To get significant results for return losses, each dielectric bridge has been made large enough. "On wafer" measurements of this structures are made, from 1 GHz to 50 GHz.

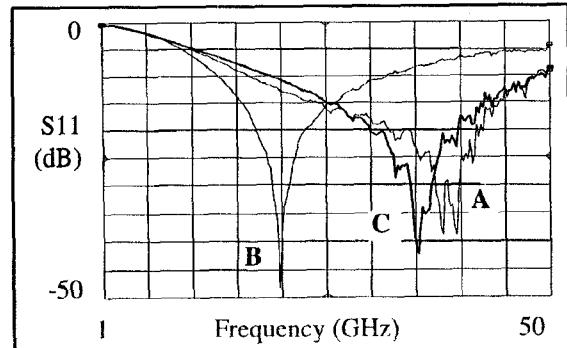

### Asymmetric resonators

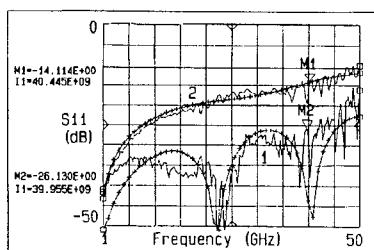

Some preliminary measurements have been made in order to verify the efficiency of the bridges for filtering the parasitic coupled slotline-mode. On the figure 6, the return losses (measurements) of asymmetric resonators are presented. Compared to the case with bounding wire (curve A), we can note the real efficiency of the dielectric bridges for filtering the parasitic mode (curve B). Obviously, according to the fact that the dielectric bridge modify the length of the resonator, we can observe a shift frequency of the response. Now by using the compensation technique, it is possible to modify the resonant frequency of the resonator (curve C).

Fig. 6 : Return losses

Fig. 7 : Assymmetric resonators

### 50 $\Omega$ transmission line

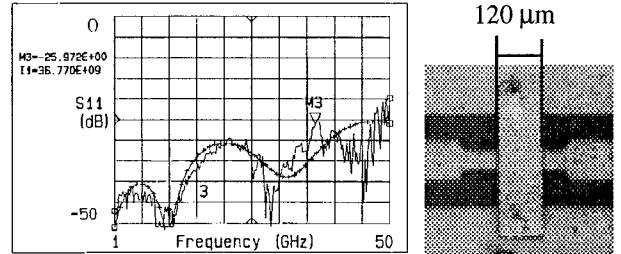

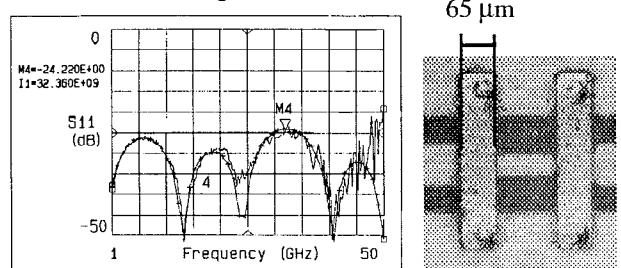

On the figure 8, the curve 1 represents the return losses of a 50  $\Omega$  multilayer CPW, and curve 2 is relative to an identical transmission line with a bridge of 135  $\mu\text{m}$  length. In this last case, it can be noted that the return losses are higher than -15 dB at 40.4 GHz. As illustrated on figures 9 and 10, the compensation permits to achieve an acceptable

return losses level. Less than -24 dB return losses are obtained at 40 GHz, for the two types of compensations (type B : curve 3) (type A : curve 4). The compensation technique doesn't give supplementary losses. The insertion losses are less than 0.7 dB. A fair agreement is observed between simulated and experimental data, keeping in mind the fact that conductor losses, dielectric losses and discontinuities were neglected in the simulations.

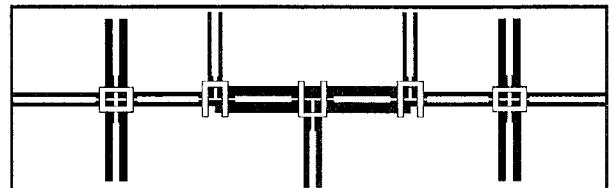

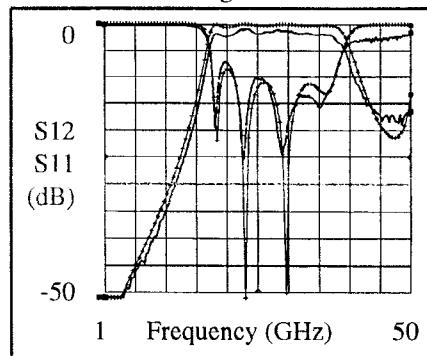

### Band pass filter

We are working on the design of basic microwave functions such as filters, for which integrated bridges are used. The topology of the filter we have chosen to study is presented on figure 11. It is a 20 - 40 GHz band-pass filter, built on alumina substrate ( $\epsilon_r = 9.6$ , thickness 635  $\mu\text{m}$ ) and composed of two symmetrical resonators and three asymmetrical resonators. The experimental response and the theoretical response of the filter are presented on the figure 12. The theoretical response include the effect of the tee junctions and of the cross junctions.

### Conclusion

Compare to the classical uniplanar technology, the principal advantage of the multilayer uniplanar technology is to get robust and reproducible integrated bridges. Indeed, with this new technology, it's possible to control the shape and the dimensions of the bridges. It is then easier to modelize their parasitic effects. Furthermore, a broadband compensation technique has been developed in order to make transparent the bridge on a CPW. The fair agreement between theoretical and experimental data shows that a static approach is sufficient (in the frequency range from 1 GHz to 50 GHz). The bridge model (through a transmission line approach) can be easily included in commercial C.A.O. software such as H.P. M.D.S.

Fig. 8

1 : 50  $\Omega$  multilayer CPW

2 : 50  $\Omega$  multilayer CPW with an uncompensated bridge

Fig.9

Fig. 10

Fig.11

Fig.12

experimental data : — theoretical data : +

### References

[1] P. BARNWELL and all High performance material technologies for advanced circuit assemblies and MCMs. Microelectronics international - Journal of ISHM Europe. n°38, Sept 1995

[2] H. E. GREEN The numerical solution of some important transmission-line problems. IEEE Trans on Microwave Theory and Technique. Vol 13, SEP 65.

[3] N.H. KOSTER and all Investigations on air bridges used for MMICs in CPW technique. Digest of the 19 th EMC. London 1989.

### Acknowledgement

The authors wish to thank the CNET of LANNION (FRANCE) for "on wafer" measurements.